本文包含以下部分,可點選快速連結(附實際操作影片)

◆ USB2.0和Ethernet測試發展和更新:USB2.0的測試與發展/Ethernet測試

◆ 智能系統內部匯流排測試:DDR匯流排測試/MIPI D-PHY匯流排測試

◆ 協議測試

◆ 關於2023年度全新升級的EXR系列示波器

◆ 使用示波器執行USB 2.0 Device眼圖測試及USB 2.0 Inrush Current實際測試影片

典型的產品設計和開發流程,通常會在批量生產和出貨前進行完整的功能性測試和一致性測試。通過嚴格的一致性測試,即可準確測量出系統相對於CTS(Compliance Test Specification)的裕量(Margin),從而為產品設計的降成本方案找到準確的方向、為產品在日益激烈的市場競爭中找到準確定位。對系統廠來說,存在成本考量,但對於IC廠是否就沒有一致性測試的動力呢? IC廠基於產業鏈的地位,一致性測試可以準確的測量出晶片產品系統化後的裕量,對下游系統廠而言則是一個最佳的案例和參考設計,也讓下游廠商有足夠的信心保證。

立刻查看

快速進行高速介面和匯流排的物理層相容性測試

詳細白皮書

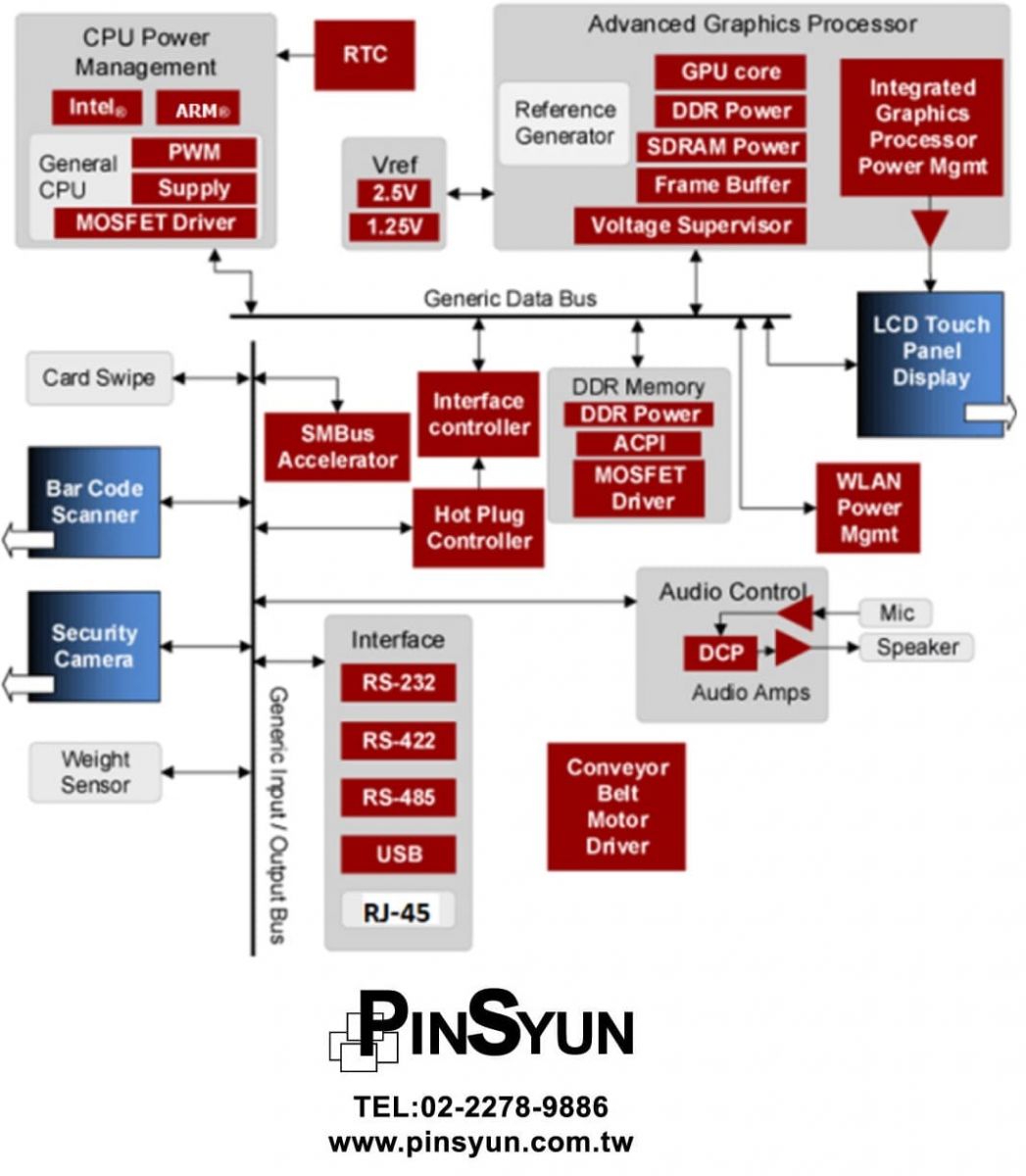

現今的智慧系統已經進入到我們生活的各個領域,從消費電子的智慧手機和手錶,到智能汽車的各種導航和自動駕駛,再到物聯網典型應用的抄表系統及POS機,甚至是未來潛在的巨大市場中的智慧家居系統等。典型系統框架圖如下,一般採用嵌入式32位處理器,典型如32位ARM處理器,當前主流採用DDR3 SDRAM作為資料記憶體,儲存程式則採用NAND Flash元件。外部配置USB2和10/100/1000 Base-T乙太網,另外還會配置一些攝影機和顯示器。此外還有一些其它的低速I/O介面,如語音和QR code辨識等功能,其它與無線應用相關介面如WiFi和藍牙之類不在本文討論中。

圖:典型智能系統框架圖

這一典型系統充分說明了“麻雀雖小,五臟俱全”的道理,為了確保性能,對其進行完備的測試也是必不可少的。測試的重點主要在於內部核心的DDR儲存匯流排存,以及重要的人機互動設備如攝像頭和螢幕所使用的主流匯流排MIPI,還有外部介面USB2和10/100/1000Base-T等。進行完備的測試是產品性能和品質的有力保證,也是產品在市場上對客戶的信心保證。本文我們就當前市場上典型的智能系統的相容性測試和內部匯流排測試做一個簡介,討論的匯流排和介面相容性測試均著重於發送端信號測試。

USB2和Ethernet作為經典的外部匯流排介面,已經在產業界應用達20年之久,測試方法也非常成熟。由於採用這兩個標準的設備種類繁多,不同種類產品之間的互聯互通和相容性測試一直是產品是否合格的判斷依據之一,因此雖然成熟但是依然不可忽視。

USB2.0的基本電氣特性如下

|

|

速度 |

幅度 |

上升時間* |

|

低速 |

1.5Mb/s |

3.3V |

75~300ns |

|

全速 |

12Mb/s |

3.3V |

4~20ns |

|

高速 |

480Mb/s |

400mV |

500ps |

* 上升時間Tr定義為10%-90%

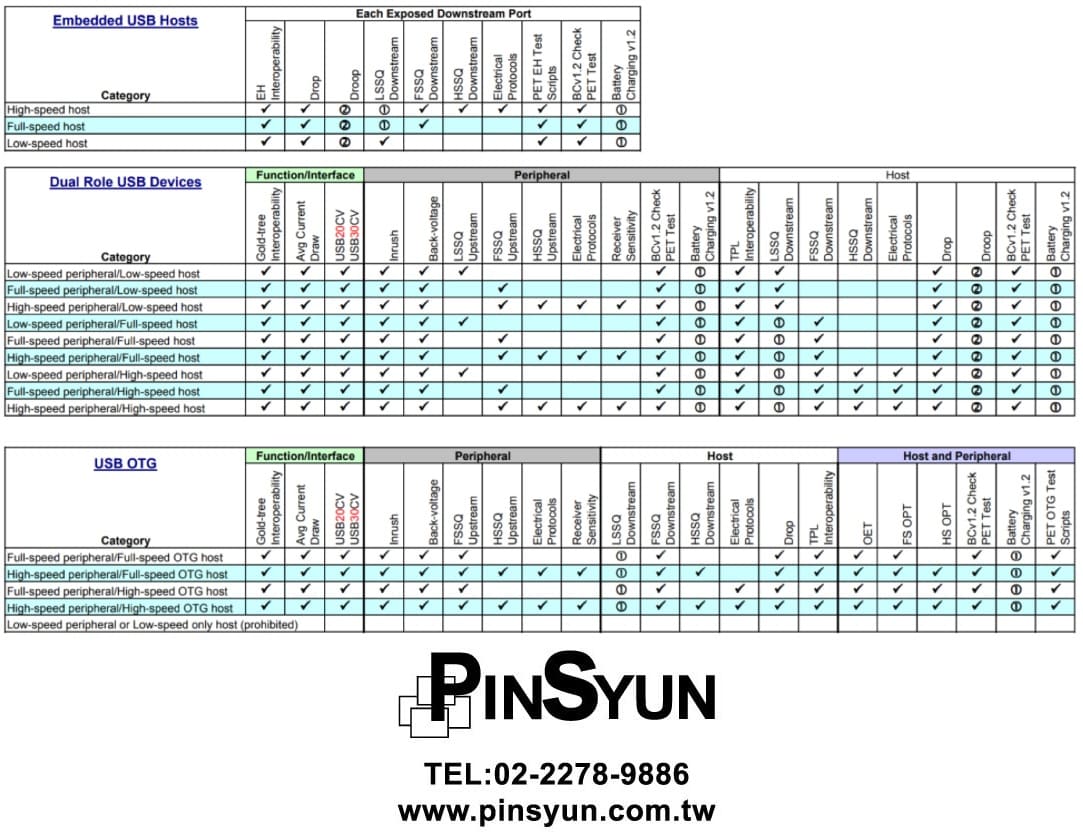

USB2介面的測試傳統上主要分為Host和Device及Hub三大類。下表為USB-IF近年更新的不同設備的測試專案清單,如果您的產品需要進行符合協會標準的測試認證則應當嚴格按照下表的測試項目進行:

圖:USB2.0 Test Matrix

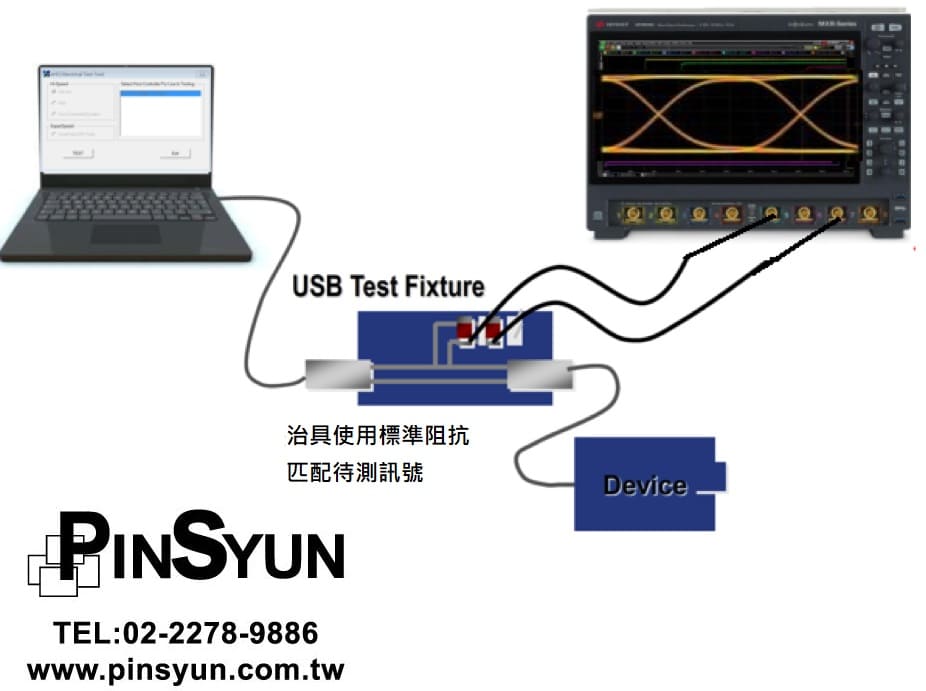

Device的SQ測試連接如下圖:

圖: USB2.0 SQ測試連接圖

Windows系統的Host測試比較簡單,但現今的智能系統多採用嵌入式系統,故一致性測試三要素之一的標準測試信號或碼型的獲取,成為相當關鍵的問題。

USB2.0測試中其實還有很多項目,詳情請登錄USB-IF協會查閱詳細測試規範:https://www.usb.org/document-library/usb-20-electrical-compliance-test-specification-version-107

USB2.0 測試需要多大頻寬的示波器?根據USB2.0 CTS最新發表的描述,會需要使用2.5GHz頻寬示波器,EXR254A/DSOS254A等2.5GHz以上的示波器才是最佳選擇,除了示波器主機外,USB2.0相容性測試軟體D9110USBP及電流探棒等配件也是必要的,立刻點我留言或右下角私訊小編洽詢詳細附件清單。

圖:最新USB2.0 CTS關於頻寬描述 |

作為電子行業另一個長期的主流標準,乙太網路一直是遠距離高速通訊的首選。主要是由科技行業協會(例如IEEE)或者國家標準(如ANSI)所定義,近期沒有太多變化,不像USB標準由業界公司主導而一直在演進。因此,10/100/1000 Base-T標準定義後就沒有太多更新和發展,而業界和科技協會一直致力於推動更高速率標準,如400G/800G。

針對傳統10/100/1000Base-T,推薦示波器頻寬依然為1GHz,相容性測試軟體型號D9010ETHC。但是反過來,近年來量測儀器一直在向前發展,例如現今的中階示波器已經基本全部實現了10bit化,而且取樣速率也比以往得到很大提高,因此測試精度比以往實際提高了很多。推薦的示波器: EXR104A/EXR108A/DSOS104A, 立刻詢價

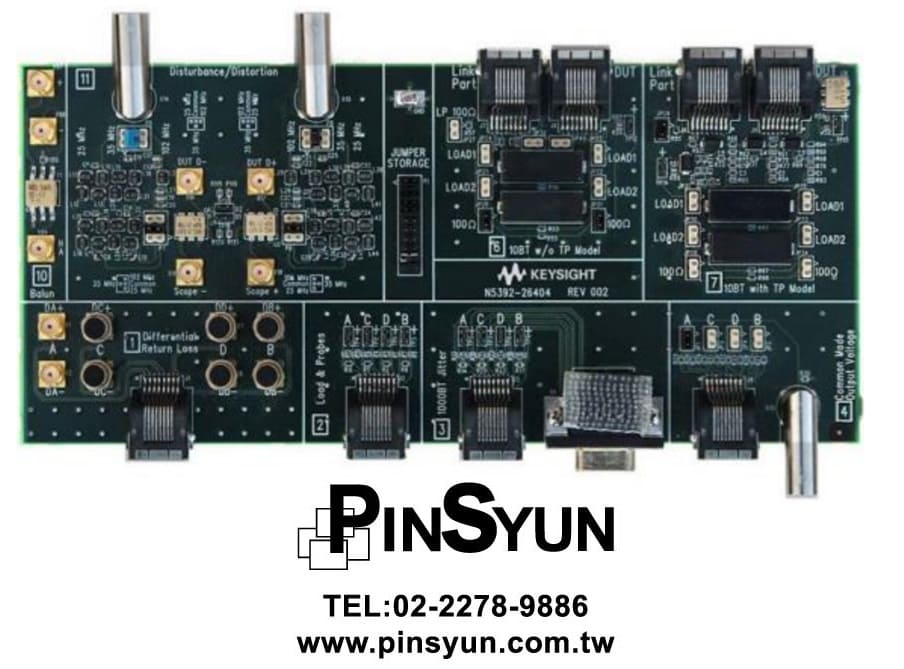

測試碼型和信號:為了進行10和1000 Base-T的測試,需要使用者自行配置PHY內的暫存器將PHY設為測試模式,以發出測試信號。而100 Base-T可透過設置暫存器或將N5395C治具上的TC6部分與Link Partner連接以自動發出測試訊號。

測試夾具N5395C:

圖:10/100/1000Base-T乙太網夾具

另外通常還需要可用於連接示波器和治具的1.5GHz差動探棒,推薦型號1130B,搭配E2678B探棒頭。當然這些配置只能完成針對發送端的基本訊號和一些抖動測試,實際上乙太網測試中還有Return Loss測試,這部分需要使用到網路分析儀。有時需要加Disturbing等類比信號進入待測物,因此還需要訊號產生器等其他量測儀器。

除了針對智能系統的10/100/1000Base-T測試外,頻寬4GHz的EXR系列示波器EXR404A搭配D9010EBZC相容性測試軟體還可以支援MGBase-T,NBase-T和10G Base-T,這些標準主要是針對桌機市場的高速通訊需求而設計。針對各乙太網標準測試,示波器的靈活頻寬升級能力尤為重要,Keysight EXR系列示波器可原機頻寬及通道數升級,讓使用者為未來的產品發展及配套的測試能力提升預留空間。

|

標準 |

頻寬需求 |

主機及軟體 |

夾具與配件 |

|

10/100/1000 BASE-T |

1 GHz |

EXR104A+D9010ETHC |

N5395C+1130B+E2678B |

|

MG/N/10G BASE-T |

4 GHz |

EXR404A+D9010EBZC |

U7237A+纜線 |

表:業界主要Ethernet標準發送端測試設備清單

USB和Ethernet作為典型的外部介面,其測試完全符合相容性測試的各種要素,因此連接環境非常簡單。然而,在現今的智慧系統中,DDR和MIPI匯流排也扮演著極為重要的角色。DDR記憶體是CPU系統的關鍵元件,確保其穩定可靠運作非常重要。而MIPI作為消費類電子行業最重要的標準協會,定義了多種標準分別用於不同部件之間的互連。當前MIPI在業界常常提及的實體層標準有D-PHY,C-PHY,M-PHY。本文從中端示波器角度出發,因此重點在D-PHY。

典型的智能系統主要採用DDR3介面,部分高速系統也會使用DDR4匯流排。與PC系統使用標準DIMM插槽記憶體條不同,智能系統通常使用嵌入式系統,因此CPU和DRAM記憶體之間的設計和開發非常考驗工程師,然而實際上很多產品在出貨時很多潛在的隱患沒有徹底解決,所以充分的測試工作還是非常重要。

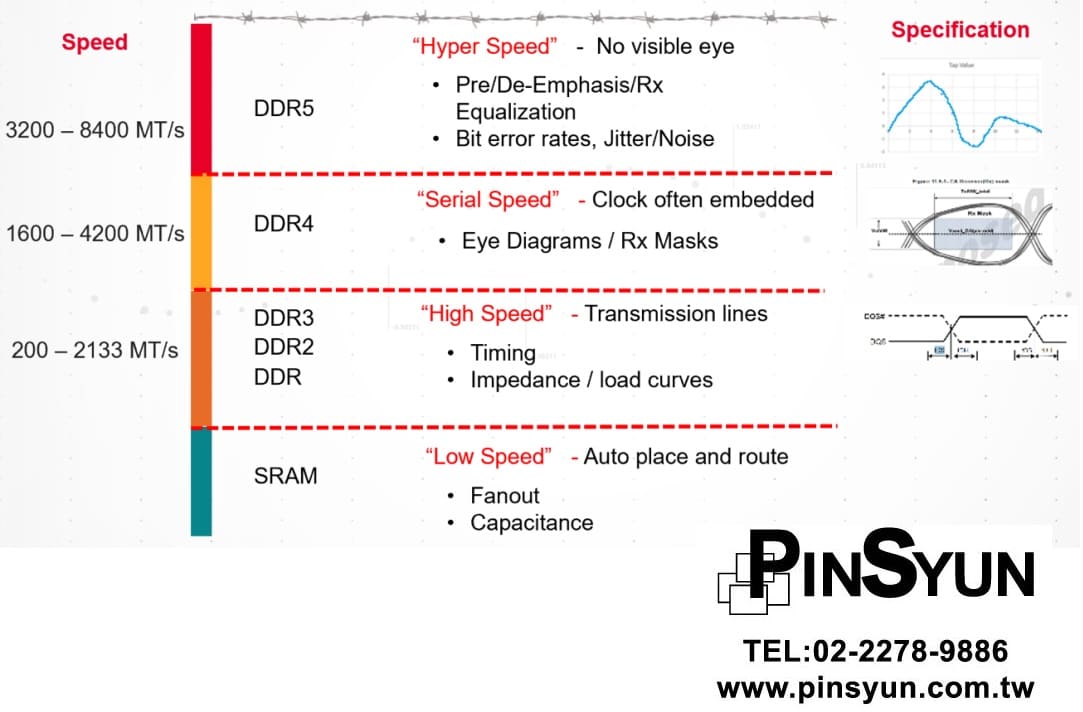

圖:當前已經在用的DDR匯流排標準速率和SI關注問題

首先,我們來看DDR3的頻寬需求。DDR3是目前主流的存儲介面,其資料速率最高可達2133MT/s,時鐘速度為1066MHz,信號上升沿最快約為100ps(20%-80%),因此BWsignal=0.4/100ps=4GHz。使用平坦回應示波器,其頻寬為BWscope=1.4BWsignal=1.44GHz=5.6GHz。另外,也可以從信號的最高切換頻率1066MHz出發,按照5倍頻寬來計算,其需求頻寬為5.3GHz,結果也相近。

從取樣速率的角度來看,對於資料最小寬度約為468ps的信號,EXR 16GSa/s提供7個取樣點,並搭配插值技術,能夠滿足信號重構的需求。因此對於DDR3 2133MT/s的信號而言,EXR系列的6GHz頻寬基本上可以符合要求。

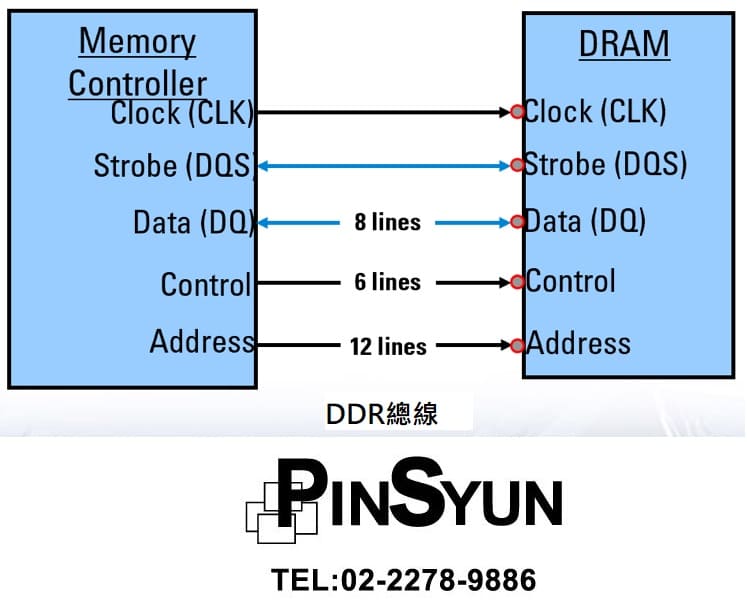

下面是DDR2/3匯流排架構示意圖。JEDEC協會作為業界記憶體行業專門協會,針對各種存儲相關介面匯流排定義了各種規範,當然DDR相關規範也在其中。

|

特別說明的是,JEDEC標準定義的讀寫信號測試點都在DRAM側信號管腳,因此,從控制器寫入DRAM的信號在傳輸鏈路的末端或接收端,而從DRAM讀出的信號則在發送端。如果ODT匹配不好或線路阻抗匹配設計不佳,則在讀取信號時反射會被放大。此外,由於從CPU或控制器傳輸到DRAM的寫信號,相比從DRAM發出的讀信號,通常幅度略低。 |

圖:DDR匯流排架構示意圖

考慮到DDR皆使用讀寫資料共用匯流排架構,而讀和寫分別涉及DRAM和CPU或控制器,因此需要對讀寫資料進行分離測試。

從以上說明,已經可以看出DDR測試中要解決的問題了。

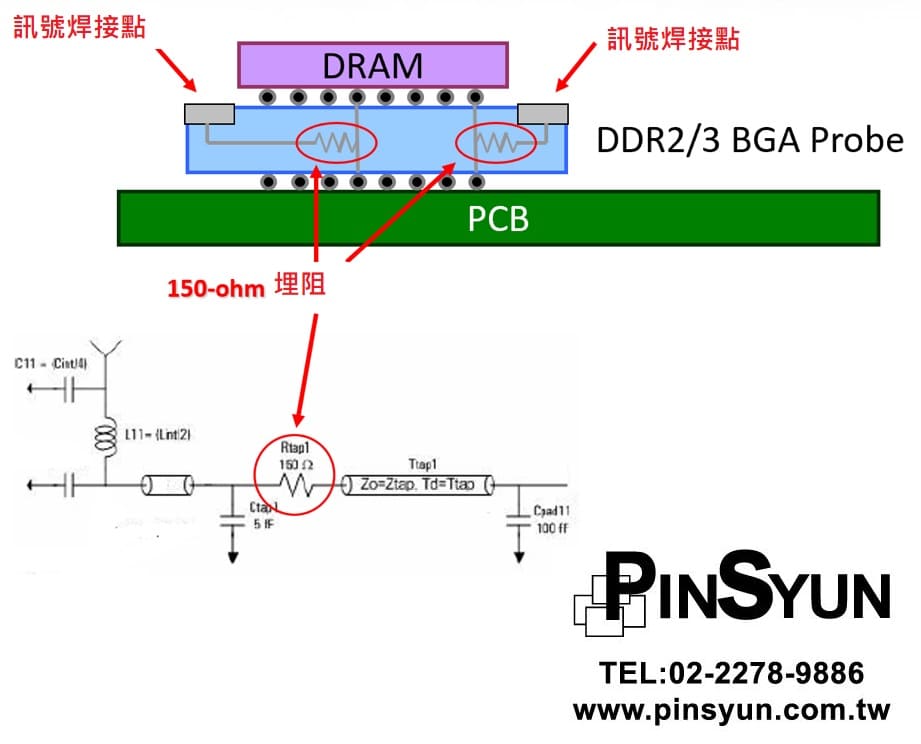

自DDR2標準開始,DRAM通常採用ODT(片上端接),因此很難找到方便且適當的測試點。通常只能在靠近DRAM顆粒的位置焊接過孔,但是如果這些預留的過孔與DRAM距離太遠,在高速傳輸下就容易產生SI問題。因此,對於1600MT/s以上的信號,使用過孔是不切實際的。

BGA Probe是一種測試工具,可用於測試DRAM信號的保真度。它是一個夾具,插在主電路板和DRAM之間,使用標準DRAM封裝,包含雙面焊球和150Ω阻尼電阻,以提取信號並連接到焊接探頭以進行測試。下圖即為BGA Probe和電路結構示意圖。

圖:DDR2/3 BGA Probe示意圖

有效的讀寫分離是準確進行DDR匯流排測試的另一個先決條件。當前主要方法有三種:

a. 程式控制法。通過程式設計分別專門進行讀或寫操作,分別對讀或寫資料進行測試。這一方法在於不能完全實現純粹的讀或寫,另外不是真實的系統運行狀態,因為真實運行的系統不可能只進行讀或寫。

b. 使用數位邏輯通道連接控制匯流排,並設置觸發進行讀寫操作分離,這是一個有效的方法,但如何連接更多的信號仍然是一個難題。

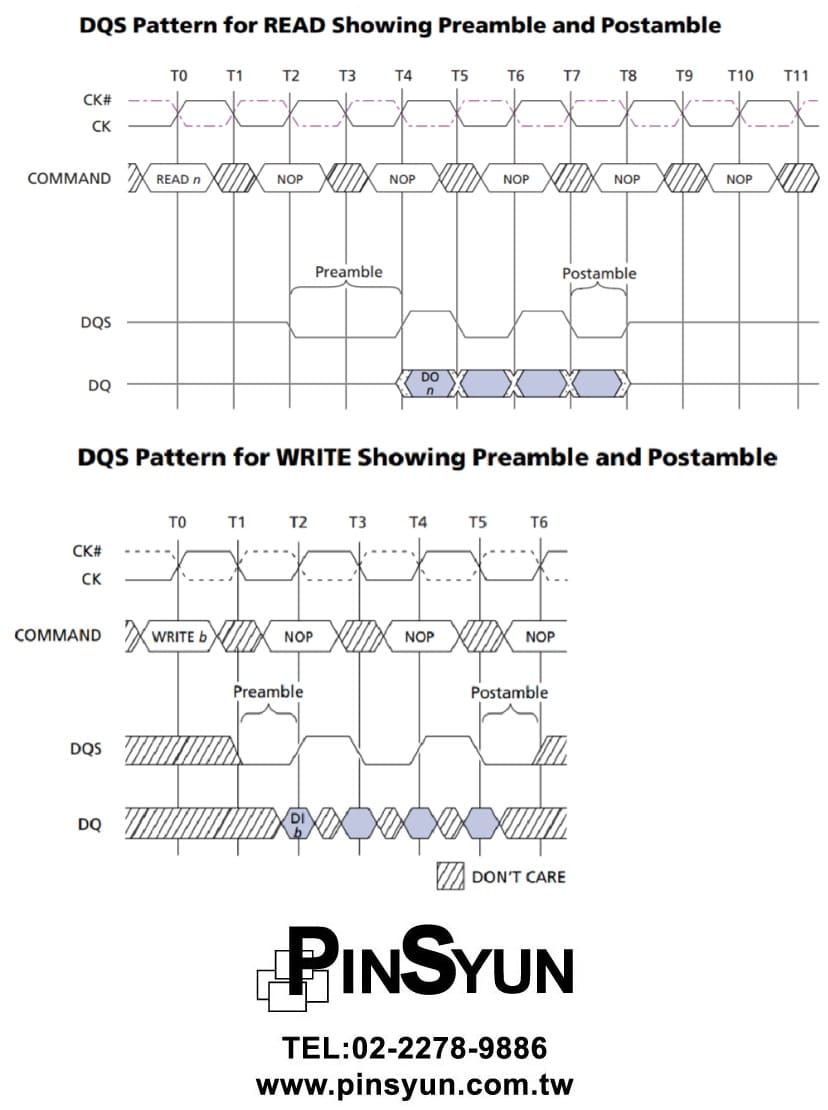

c. 使用區域觸發(InfiniiScan Zone Trigger)功能。透過是德科技讀有的區域觸發功能,可依讀寫訊號前導碼及訊號幅度的不同進行區隔,其中讀取Preamble為完整週期,寫入則為半個週期,且寫入信號的幅度通常較讀取信號略低。InfiniiScan Zone Qualify Trigger只需要簡單的根據波形差異畫框,即可實現“所見即所得”式觸發,最多可以定義8個區域。

影片:在 Keysight Infiniium 示波器上使用區域觸發功能 |

另外,Keysight提供的DDR3測試軟體,也會自動調用區域觸發功能(InfiniiScan Zone Trigger)來進行高效的讀寫分離,更加快速的完成測試。

圖:DDR3 匯流排DQS Read/Write Preamble 差異(Source from Micron)

圖:InfiniiScan Zone Qualify Trigger 用於DDR匯流排讀寫分離動示意圖

另外要說明的是,DDR2/3標準已經發佈了很多年,對其信號完整性測試,除了在信號幅度的電氣特性方面外,主要是信號以及信號之間的時序和參數,其本質主要就是建立/保持時間(Setup/Hold)的測試。因此要進行完整的測試,示波器必須支援建立/保持觸發。

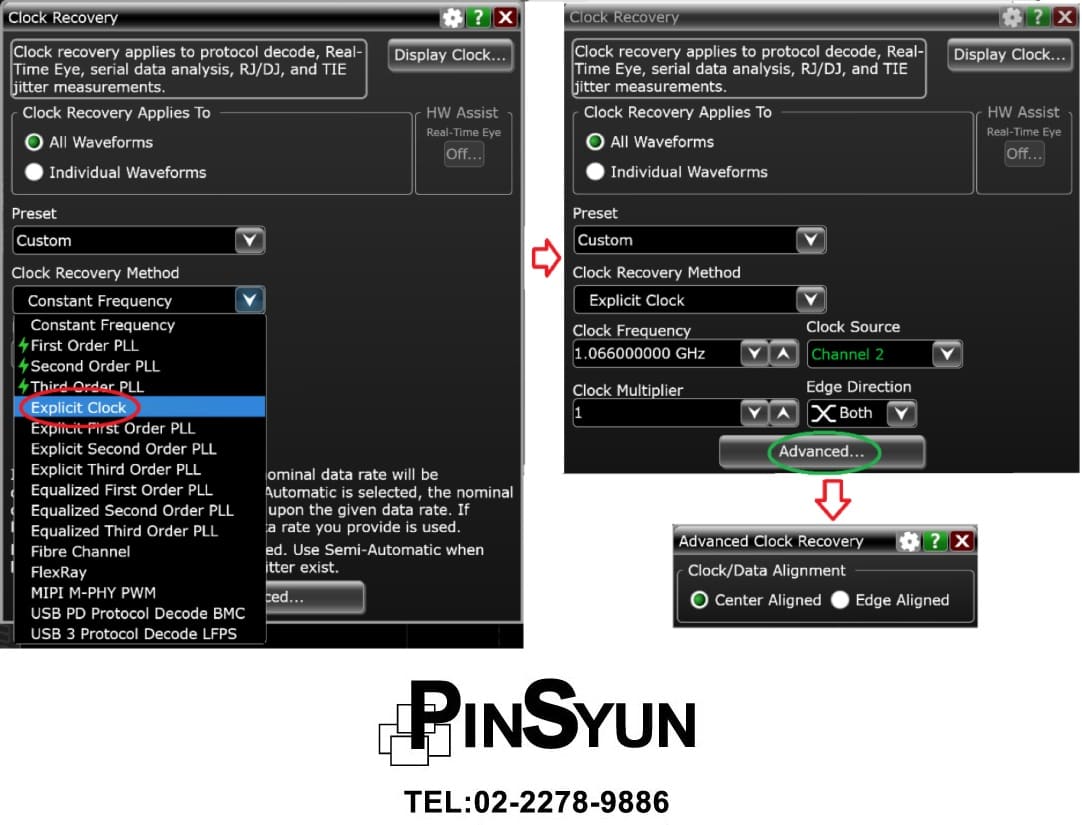

隨著串列資料眼圖分析的普及,DDR2/3眼圖測試也開始流行起來,不過不是被規範所定義的。需要補充說明的是,手動進行眼圖測試必須設置時脈還原。針對DDR匯流排類眼圖測試,使用外部時鐘Explicit Clock,具體設置如下圖所示。在讀寫DQS和DQ時,需分別進行邊緣和中心對齊,並需要手動設置中心對齊或邊緣對齊。

圖:DDR匯流排眼圖測試時脈還原手動設置示意圖

|

以上簡單介紹了DDR測試中的一些問題以及解決方法,Keysight提供全面的DDR2/3匯流排測試軟體: |

MIPI是當今個人消費電子領域最成功的標準之一,成功的從智能手機擴展到各種終端系統。在物理層面上,目前主要有D-PHY、C-PHY和M-PHY三種標準。此外,在2020年6月3日,MIPI協會還宣布了A-PHY標準,支持最高15米的傳輸距離,速率分為5檔,從2Gbps到16Gbps,為跨越整個車輛的資料傳輸提供實體層基礎,為智慧網聯汽車市場的ADAS和ADS系統中的攝影機和顯示螢幕提供底層支援。

下圖為MIPI協會各標準分層架構和應用對應圖。其中D-PHY主要用於CSI和DSI,分別對應攝影機和顯示幕。當前在典型智能系統中,主要使用的標準是D-PHY V1.1以下,速率在1.5Gbps以下,V1.2支撐2.5Gbps未來將得到更廣泛應用。D-PHY標準近幾年也得到了長期的發展,D-PHY3.0最高支援速率高達14Gbps。本文,我們將著重於D-PHY1.2以下測試的介紹。

圖:MIPI標準分層架構和應用對應圖

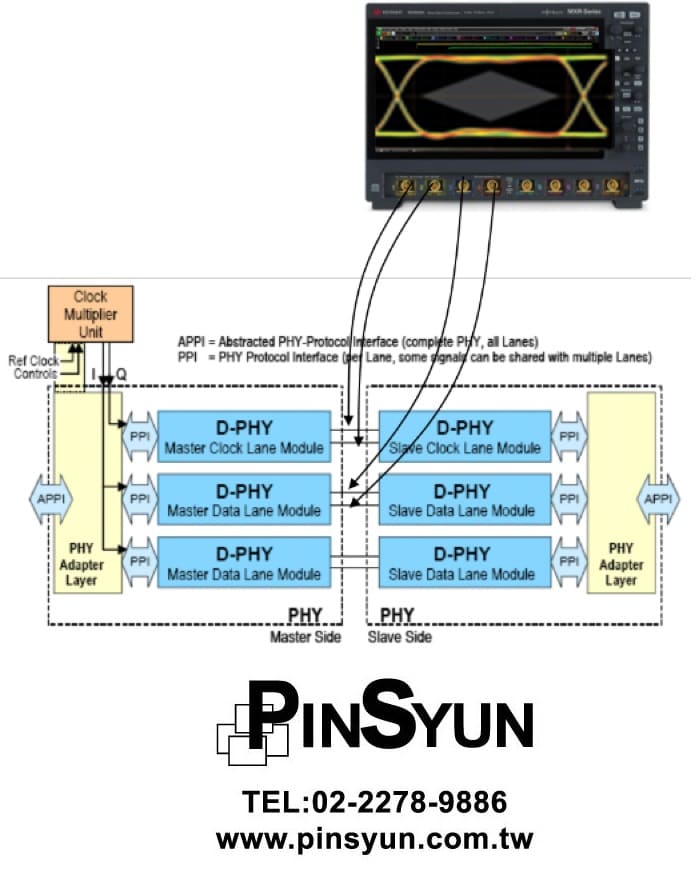

D-PHY標準於2003年推出,採用當時的技術條件並吸收了多種標準的特點,如類似LVDS訊號、差動訊號帶外部時鐘同步並支援1、2、4鏈路切換等。為了降低功耗,D-PHY採用LP和HS兩種工作模式,時鐘頻率類似DDR標準只有資料速率的一半,以降低時鐘帶來的干擾。另外,為了方便在LP和HS模式之間切換,D-PHY還採用了特殊的電路結構,並在HS模式信號上添加了共模偏置電壓。這些因素都增加了D-PHY標準的測試複雜度。

和DDR匯流排類似,D-PHY的測試也不同於介面測試。對於系統產品,除非專門為晶片研發開發測試板,否則通常無法斷開攝像頭與處理器之間的CSI介面,或者斷開處理器與屏幕之間的DSI介面。換言之,針對系統產品進行D-PHY測試時無法使用夾具,必須使用探頭焊接進行測試。

圖:D-PHY測試接線圖

考慮到HS模式下訊號上的共模偏置電壓VCMTX相關參數測試要求,必須分別對資料DP和DN分別測試以得到共模和差動訊號,因此D-PHY測試需要3-4組差動探棒。如果只使用3組探棒,針對CLK的共模測試會需要分兩次焊接,一次差動焊接輔助完成Data測試,另外還要再專門對CLKP和CLKN進行分開焊接測試CLK的共模偏置電壓。因此,建議使用4組探棒,可以同時焊接完成一組DP+DN/CLKP+CLKN的測試,以達到最高的測試效率。

D-PHY的測試信號,當然是非常容易解決,只需攝影機一直在工作或者播放圖片或視頻到顯示幕上即可。

如何選擇一款合適的示波器來進行D-PHY 1.2訊號測試?針對D-PHY 1.2 2.5Gbps以下速率,哪個頻寬比較適合?而對於MIPI D-PHY 1.5Gbps以上速率的晶片開發,需要全面驗證測試件的功能並在各種可能情況下測試性能。建議使用13GHz以上頻寬的示波器,如Infiniium V或UXR系列。 |

1. 可測性設計(Design for Test)。

由於D-PHY測試大量使用單端訊號進行差分和共模信號的運算,因此信號的接地回路必須非常短,否則共模測試將面臨極大的困難。在設計電路時,應考慮在資料和時鐘信號接近的位置預留方便可靠的接地。

2. 探棒頭焊接

使用焊接探棒頭如E2677B,為了方便連接,有時不得不使用較長的電阻絲線,但是阻尼電阻應儘量靠近訊號測試點,以免Stub過長。

相容性測試作為即時示波器的最廣泛的用途,是很多產品出貨前認證測試的必經項目。在執行並通過業界標準的測試方法後,即可貼上標準Logo,不僅是產品品質的保證,也是在市場的通行證。 EXR系列多通道示波器,頻寬涵蓋500MHz~6GHz,提供業界當前主流的所有中等訊號速率標準的一致性測試,包括(但不限於):

| 匯流排標準 | 推薦頻寬 | 示波器 | 搭配選配 |

| USB 2.0 | 2 GHz | EXR204A | D9010USBC |

| 10/100/1000 Base-T | 1 GHz | EXR104A | D9010ETHC |

| 10G/MG/NG Base-T | 4 GHz | EXR404A | D9010EBZC |

| Automotive Ethernet | 1 GHz | EXR104A | AE6910T |

| DDR2/LPDDR2 | 4 GHz | EXR404A | D9020DDRC |

| DDR3/LPDDR3, up to 1866M T/s | 6 GHz | EXR604A | D9030DDRC |

| MIPI D-PHY, up to 2.5 Gbps | 6 GHz | EXR604A | D9010DPHC |

| MIPI C-PHY, up to 2.5Gbps | 6 GHz | EXR604A | D9010CPHz |

本文針對四個主要介面和匯流排標準相容性測試的一些問題和關鍵細節做簡單說明,因為篇幅有限,無法分別進行詳細描述。補充說明,每個標準的測試軟體都支援自動化測試,提供按照 Setup → Select → Config → Run 的標準流程,並最終給出測試報告。報告裡會專門對每個測試專案的結果標明Pass/Fail,並參照規範給出剩餘的裕量,以提供進一步改進設計或者降成本的依據。

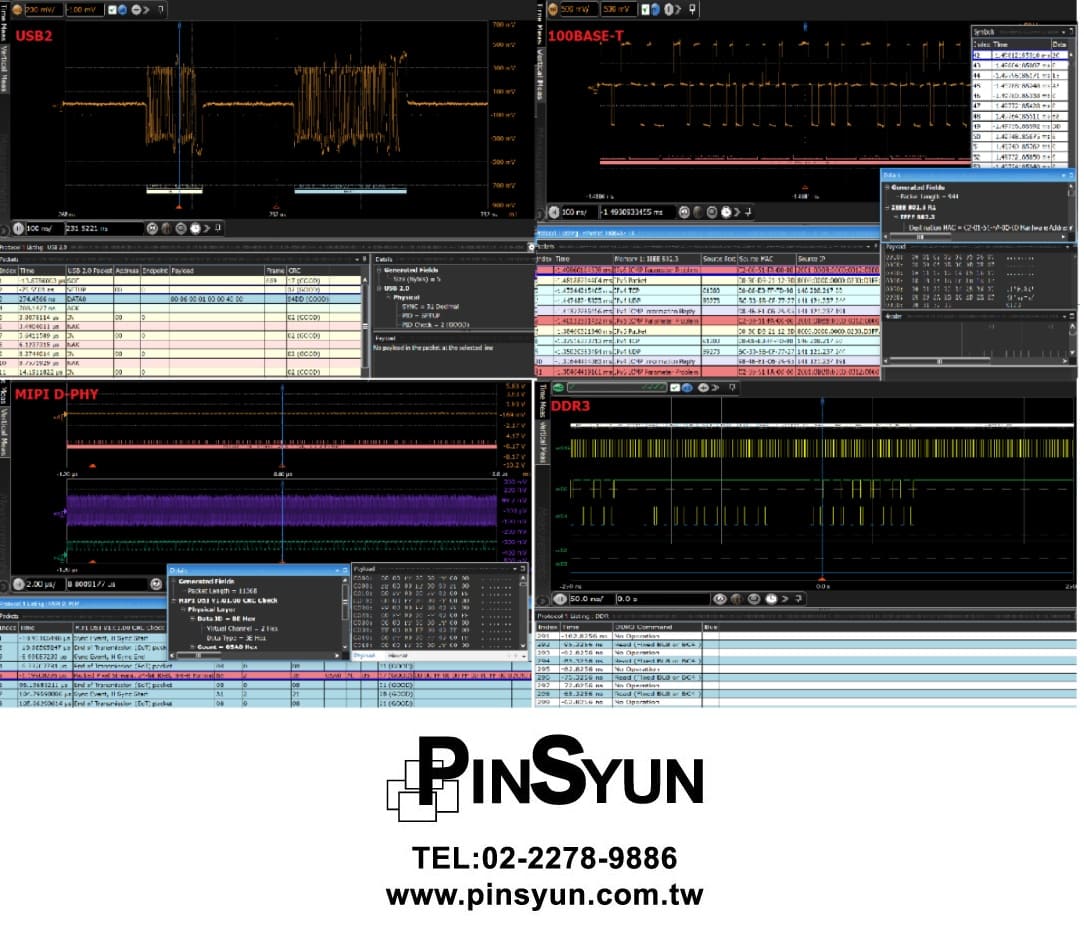

針對上述標準,還提供了強大的協議解碼和觸發功能,如下圖,協議觸發和解碼功能為這些匯流排的測試提供了強大的輔助工具。除了標準的一致性測試,EXR 6GHz型號對智能系統中也會涉及的HDMI1.4b,PCIE1.x,SATA 1.5G/3.0Gbps,Rapid IO等速率在4Gbps以下訊號也可以支援。

圖:USB2/100BASE-T/D-PHY/DDR3協議觸發和解碼

EXR系列示波器作為一款多通道的7合1產品,在2023年度全新升級,添加4GHz及6GHz機型!除了提供功能強大的測試軟體外,還有電源紋波、雜訊測試以及PMIC上電時序測試能力。搭配電源量測軟體套件,可在 EXR 系列示波器上執行各種自動化電源供應器量測,包括執行控制迴路響應和 電源拒斥比 (PSRR) 量測所需的獨特頻率響應分析。輕鬆完成三相交流電機的電壓、電流、功率品質、電流諧波等電源分析。

內建獨有的除錯獵人(Fault Hunter)功能,可自動偵測並快速定位罕見或隨機的異常訊號。只要按一下按鈕,示波器便可對輸入訊號進行 60 秒的統計量測分析,並自動啟動進階觸發功能,以針對正常訊號及異常訊號進行比對,偵測出隱藏的異常訊號。測試失敗的結果會自動儲存在記憶體中,可複製故障條件再次進行觸發, 此除錯獵人功能可加快設計和縮短發現隨機錯誤的除錯時間,並顯著地改善測試工作流程。甚至透過遠端團隊協作,工程師可快速發現問題、找出根源、提出解決方案,進而縮短產品上市時間並降低人力成本。

影片:在 Keysight Infiniium 示波器上使用 Fault Hunter |

▲ 立刻留言詢價或私訊小編,成功預約展示即可獲得三合一充電線!

快速進行高速介面和匯流排的物理層相容性測試

* 查看產品介紹:Keysight EXR系列示波器規格總覽

* 相關研討會:[實作研討會] 快速入手訊號分析及相容性測試-Keysight示波器實機量測研習營

獲得第一手消息 ! 立即訂閱

獲得第一手消息 ! 立即訂閱